2.3. Цикли обміну інформацією

2.3.1. Цикли програмного обміну

Розглянемо для прикладу два досить типових випадку програмного обміну по магістралі мікропроцесорної системи.

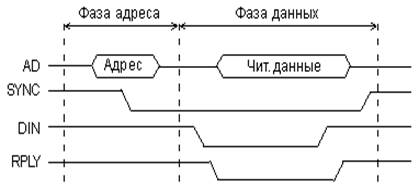

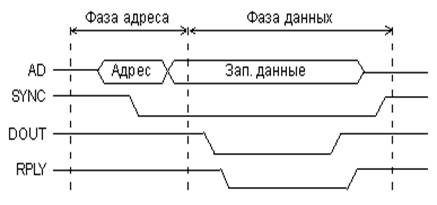

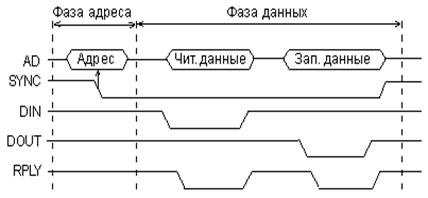

Перший приклад - це обмін по мультиплексованій асинхронній магістралі Q-bus, запропонованою фірмою DEC і широкозастосовуваною в мікрокомп'ютерах і промислових контроллерах. Спрощені тимчасові діаграми циклів читання (вводу) і запису (виводу) по цій магістралі приведені на мал. 2.3 і 2.4.

Відзначимо, що в подальшому тексті знак «мінус» перед назвою сигналу говорить про те, що активний рівень сигналу низький, пасивний - високий, тобто сигнал негативний. Якщо мінуса перед назвою сигналу немає, то сигнал позитивний, його низький рівень пасивний, а високий - активний.

На шині адреса/данных (AD) на початку циклу обміну (у фазі адреси) процесор (задатчик) виставляє код адреси. На цій шині використовується негативна логіка. Середній рівень сигналів на шині AD означає, що стани сигналів на шині в дані тимчасові інтервали не важливі. Для стробування адреси використовується негативний синхросигнал -SYNC, що виставляється також процесором. Його передній (негативний) фронт відповідає дійсності коду адреси на шині AD. Фаза адреси однакова в обох циклах запису і читання.

Мал. 2.3. Цикл читання на магістралі Q-bus.

Одержавши (розпізнавши) свій код адреси, пристрій вводу/виводу або пам'ять (виконавець) готується до проведення обміну. Через деякий час після початку (негативного фронту) сигналу -SYNC процесор знімає адресу і починає фазу даних.

Мал. 2.4. Цикл запису на магістралі Q-bus.

У фазі даних циклу читання (мал. 2.3) процесор виставляє сигнал строба читання даних -DIN, у відповідь на який пристрій, до якого звертається процесор (виконавець), повинен виставити свій код даних (читані дані). Одночасно цей пристрій повинен підтвердити виконання операції сигналом підтвердження обміну -RPLY.

Для сигналу -RPLY використовується тип вихідного каскаду ОК, щоб не було конфліктів між пристроями-виконавцями. Процесор, одержавши сигнал -RPLY, закінчує цикл обміну. Для цього він знімає сигнал -DIN і сигнал -SYNC. Пристрій-виконавець у відповідь на зняття сигналу -DIN повинен зняти код даних з шини AD і закінчити сигнал підтвердження -RPLY. Після цього процесор знімає сигнал -SYNC.

У фазі даних циклу запису (мал. 2.4) процесор виставляє на шину AD код записуваних даних і супроводжує його негативним сигналом строба запису даних -DOUT. Пристрій-виконавець повинен по цьому сигналу прийняти дані від процесора і сформувати сигнал підтвердження обміну -RPLY. Процесор, одержавши сигнал -RPLY, закінчує цикл обміну. Для цього він знімає код даних з шини AD і сигнал -DOUT. Пристрій-виконавець у відповідь на зняття сигналу -DOUT повинен закінчити сигнал підтвердження -RPLY. Після цього процесор знімає сигнал -SYNC.

Тобто на даній магістралі адреса передається синхронно (без підтвердження його отримання виконавцем), а дані передаються асихронно, з обов'язковим підтвердженням їх видачі або прийому виконавцем. Відсутність сигналу підтвердження -RPLY протягом заданого часу сприймається процесором як аварійна ситуація. У принципі можлива і асинхронна передача адреси, що збільшує надійність обміну, хоча може знижувати його швидкість.

Крім циклів читання і запису на магістралі Q-bus використовуються також і цикли типу «ввід-пауза-вивід» («читання-модифікація-запис»). Спрощена тимчасова діаграма цього циклу представлена на мал. 2.5.

Мал. 2.5. Цикл «ввод-пауза-висновок» на магістралі Q-bus.

В цьому циклі адресна фаза проводиться аналогічно як, як і в циклах читання (вводу) і запису (виводу). Але у фазі даних процесор проводить спочатку читання із заданої в адресній фазі адреси, а потім запис на ту ж саму адресу. Для читання використовується строб читання -DIN, а для запису - строб запису -DOUT. У відповідь на сигнал -DIN пристрій-виконавець видає свої дані на шину AD, а по сигналу -DOUT - приймає дані з шини AD. Як і в циклах читання і запису, пристрій-виконавець підтверджує виконання кожної операції сигналом підтвердження -RPLY. Зрозуміло, що цикл «ввід-пауза-вивід» вимагає більше часу, ніж кожний з циклів читання або запису, але менше часу, ніж два послідовно проведених циклу читання і запису (оскільки для нього потрібна тільки одна адресна фаза). Сигнал -SYNC виробляється процесором на початку циклу «ввід-пауза-вивід» і тримається до закінчення всього циклу.

Як другий приклад розглянемо цикли обміну на синхронній немультиплексованій магістралі ISA (Industrial Standard Architecture), запропонованою фірмою IBM і широковикористовувною в персональних комп'ютерах. Спрощені цикли запису в пристрій вводу/виводу і читання з пристрою вводу/виводу приведені на мал. 2.6 і 2.7.

Обидва цикли починаються з виставляння процесором (задатчиком) коду адреси на шину адреси SA (логіка на цій шині позитивна). Адреса залишається на шині SA до кінця циклу. Фаза адреси, однакова для обох циклів, закінчується з початком строба обміну даними -IOR або -IOW. Протягом фази адреси пристрій-виконавець повинен прийняти код адреси і розпізнати або не розпізнати його. Якщо адреса розпізнана, виконавець готується до обміну.

У фазі даних циклу читання (мал. 2.6) процесор виставляє негативний сигнал читання даних з пристрою вводу/виводу -IOR. У відповідь на нього пристрій-виконавець повинен видати на шину даних SD свій код даних (читані дані). Логіка на шині даних позитивна. Через встановлений час строб обміну -IOR знімається процесором, після чого знімається також і код адреси з шини SA. Цикл закінчується без урахування швидкодії виконавця.

Мал. 2.6. Цикл читання з УВВ на магістралі ISA.

Мал. 2.7. Цикл запису в УВВ на магістралі ISA.

Але так відбувається тільки у разі основного, синхронного обміну. Окрім нього на магістралі ISA також передбачена можливість асинхронного обміну. Для цього застосовується сигнал готовності каналу (магістралі) I/O CH RDY. Тип вихідного каскаду для даного сигналу - ОК, для запобігання конфліктів між пристроями-виконавцями. При синхронному обміні сигнал I/O CH RDY завжди позитивний. Але повільний пристрій-виконавець, що не може працювати в темпі процесора, може цей сигнал зняти, тобто зробити нульовим відразу після початку строба обміну. Тоді процесор до того моменту, поки сигнал I/O CH RDY не стане знову позитивним, припиняє завершення циклу, продовжує строб обміну. Звичайно, дуже велика тривалість цього сигналу розглядається як аварійна ситуація. Для простоти розуміння можна вважати, що пристрій-виконавець формує в даному випадку негативний сигнал неготовності завершити обмін. На час цього сигналу обмін на магістралі припиняється.

Принципова відмінність асинхронного обміну по магістралі ISA від асинхронного обміну по магістралі Q-bus полягає в наступному. Якщо у разі Q-bus сигнал підтвердження обов'язковий, і його повинен формувати кожний виконавець, то у разі ISA сигнал про неготовність виконавець може не формувати, якщо він встигає працювати в темпі процесора. Зате у разі Q-bus до кінця циклу обміну процесор завжди упевнений, що пристрій-виконавець виконав необхідну операцію, а у разі ISA такої упевненості немає.

У фазі даних циклу запису по магістралі ISA (мал. 2.7) процесор виставляє на шину даних SD код записуваних даних і супроводжує їх стробом запису даних в пристрій вводу/виводу -IOW. Одержавши цей сигнал, пристрій-виконавець повинен прийняти з шини SD код записуваних даних. Якщо він не встигає зробити це в темпі процесора, то він може зняти на потрібний час сигнал I/O CH RDY після отримання переднього фронту сигналу -IOW. Тоді процесор припинить закінчення циклу запису.

Розглянуті приклади, звичайно, не розкривають всієї тонкості обміну по згаданих магістралях. Вони всього лише ілюструють головні принципи обміну по них.

2.3.2. Цикли обміну по перериваннях

Цикли обміну в режимі переривань будуються за тими ж принципами, що і цикли програмного обміну, але мають ряд специфічних особливостей.

Переривання в мікропроцесорних системах бувають двох основних типів:

- векторні переривання, які вимагають проведення циклу читання по магістралі;

- радіальні переривання, які не вимагають ніякого циклу обміну по магістралі.

Річ у тому, що переривань в мікропроцесорній системі звичайно буває багато. Тому процесору необхідна інформація про номер (або, як ще говорять, про адресу вектора) конкретного переривання. Ця інформація може бути передана процесору двома шляхами.

При векторному перериванні код номера переривання передається процесору тим пристроєм вводу/виводу, яке дане переривання викликало. Для цього процесор проводить цикл читання по магістралі, і по шині даних одержує код номера переривання. Шина адреси в даному циклі звичайно не використовується, оскільки пристрій, що запитав переривання, і так знає, що процесор звертатиметься саме до нього. В цьому випадку в магістралі достатньо всього однієї лінії запиту переривання для всіх пристроїв вводу/виводу. Такі організовані переривання, наприклад, в магістралі Q-bus.

Мал. 2.8. Сигнали запиту і надання переривання в магістралі Q-bus.

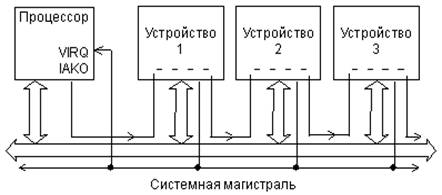

Схема розповсюдження сигналів, що беруть участь в перериваннях на магістралі Q-bus, показана на мал. 2.8. Спрощена тимчасова діаграма циклу запиту і надання магістралі представлена на мал. 2.9.

Мал. 2.9. Цикл запиту/надання векторного переривання на магістралі Q-bus.

Запит переривання здійснюється негативним сигналом -VIRQ, який може формуватися кожним з пристроїв, що запрошують переривання. Тип вихідного каскаду для цього сигналу - ОК, щоб уникнути конфліктів між пристроями, що запрошують переривання . Одержавши сигнал -VIRQ, процесор надає переривання (закінчивши заздалегідь виконання поточної команди). Для цього він виставляє сигнал читання даних -DIN і сигнал надання переривання IAKO. Цей сигнал IAKO послідовно проходить через всі пристрої, які можуть запрошувати переривання. Якщо сигнал переривання дойде до пристрою що запросив переривання, то він не пропускає через себе цей сигнал. В результаті виходить, що якщо переривання одночасно запитали два або більш пристроїв, то сигнал надання переривання одержить тільки один пристрій, а саме той, який ближче до процесора. Такий механізм дозволу конфліктів називається іноді географічним пріоритетом (або ланцюговим пріоритетом, Daisy Chain). Одержавши сигнал IAKO, пристрій, що запитав переривання, повинен зняти свій сигнал -VIRQ.

Потім процесор проводить цикл безадресного читання номера переривання. У відповідь на одержані сигнали -DIN і IAKO пристрій, якому надано переривання, повинен видати на шину адреса/данных AD код номера переривання (адреси вектора переривання) і виставити сигнал підтвердження -RPLY. Процесор читає код номера переривання і закінчує цикл безадресного читання зняттям сигналів -DIN і IAKO.

Мал. 2.10. Структура зв'язків для організації радіальних переривань на магістралі ISA.

При радіальному перериванні в магістралі є стільки ліній запиту переривання, скільки всього може бути різних переривань. Тобто кожний пристрій вводу/виводу, що бажає використовувати переривання, подає сигнал запиту переривання по своїй окремій лінії. Процесор дізнається про номер переривання по номеру лінії, по якій прийшов сигнал запиту переривання. Ніяких циклів обміну по магістралі при цьому не вимагається. У разі радіальних переривань в систему звичайно включається додаткова мікросхема контролера переривань, що обробляє сигнали запитів переривань. Саме так організовані переривання, наприклад, в магістралі ISA.

Спрощена структура зв'язків між пристроями, що беруть участь в обміні по перериваннях, на магістралі ISA показана на мал. 2.10. Процесор спілкується з контролером переривань як по магістралі (щоб задати йому режими роботи), так і зовні магістралі (при обробці запитів на перериванню). Сигнали запитів переривань IRQ розподіляються між всіма пристроями магістралі. На кожну лінію IRQ доводиться один пристрій. Тип вихідного каскаду для цих ліній - 2С, оскільки конфлікти тут не передбачені. Запитом переривання є передній, позитивний фронт сигналу IRQ. При одночасному надходженні сигналів IRQ від декількох пристроїв порядок їх обслуговування визначається контролером переривань.

Який тип переривань кращий - векторний або радіальний?

Векторні переривання забезпечують системі велику гнучкість, в системі їх може бути дуже багато. Та зате вони вимагають додаткових апаратурних вузлів у всіх пристроях, що запрошують переривання, для обслуговування циклів безадресного читання.

Радіальних переривань в системі звичайно не дуже багато (від 1 до 16). При цьому типі переривань, як правило, потрібно вводити в систему спеціальний контролер переривань. Кожне радіальне переривання вимагає вводу додаткової лінії в шину управління системної магістралі. Але працювати з радіальними перериваннями простіше, оскільки все зводиться тільки до вироблення єдиного сигналу IRQ, і ніяких циклів обміну по магістралі не вимагається.

2.3.3. Цикли обміну в режимі ПДП

Цикли обміну в режимі прямого доступу до пам'яті виконуються за тими ж правилами, що і цикли програмного обміну, і цикли надання переривань.

Перш ніж почати обмін в режимі ПДП, пристрій, якому необхідний ПДП, повинен запитати ПДП і одержати його. Процедура запиту і надання ПДП дуже схожа на процедуру запиту і надання переривання. В обох випадках пристрій, що вимагає обслуговування, посилає сигнал запиту процесору. Проте у разі ПДП процесор обов'язково повинен надати ПДП пристрою, що запитав, за допомогою спеціальних сигналів, оскільки на час ПДП процесор відключається від магістралі. А при радіальних перериваннях надання переривання від процесора не потрібно.

На магістралі Q-bus запит і надання ПДП організовуються подібно запиту і наданню переривання. Спрощена структура зв'язків пристроїв, що беруть участь в ПДП, показана на мал. 2.11. Тимчасова діаграма запиту/надання ПДП дуже близька до тимчасової діаграми запиту/надання переривання (див. мал. 2.9).

Мал. 2.11. Структура зв'язків запиту/надання ПДП на магістралі Q-bus.

Сигнал запиту ПДП, званий -DMR, передається всіма пристроями, потребуючими в ПДП, по одній лінії магістралі. Тип вихідного каскаду на цій лінії - ОК. Процесор, одержавши сигнал -DMR, видає сигнал надання ПДП DMGO, аналогічний сигналу IAKO. Цей сигнал також проходить через всі пристрої послідовно, внаслідок чого ПДП одержує тільки той пристрій, який знаходиться ближче до процесора (географічний пріоритет). А потім пристрій ПДП, що викликав його, проводить цикли обміну по магістралі, аналогічно циклам програмного обміну. В циклах ПДП інформація читається з пам'яті і записується в пристрій вводу/виводу, або навпаки - читається з пристрою вводу/виводу і передається в пам'ять.

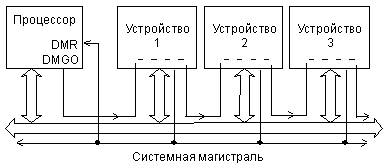

На магістралі ISA запит/надання ПДП дуже нагадує організацію радіальних переривань (мал. 2.12). Так само в системі існує контролер ПДП, до якого сходяться сигнали запиту ПДП, звані DRQ, і від якого розходяться сигнали надання ПДП, звані -DACK. До кожного каналу ПДП (пара сигналів DRQ і -DACK) підключається тільки один пристрій, що запрошує ПДП. Тип вихідних каскадів для цих сигналів -2С. Пристрій, потребуючий ПДП, посилає сигнал запиту DRQ і одержує у відповідь сигнал надання -DACK. Після цього контролер ПДП проводить цикли обміну по магістралі між пристроєм вводу/виводу і пам'яттю.

Спрощена тимчасова діаграма циклів ПДП на магістралі ISA показана на мал. 2.13.

На магістралі ISA використовуються роздільні строби запису в пам'ять (-MEMW) і записи в пристрої вводу/виводу, а також роздільні строби читання з пам'яті (-MEMR) і читання з пристроїв вводу/виводу (-IOR). Це дозволяє за один цикл обміну ПДП читати інформацію з пам'яті і записувати її в пристрій вводу/виводу або ж читати інформацію з пристрою вводу/виводу і записувати її в пам'ять. При цьому на шині адреси виставляється адреса пам'яті, а адреса пристрою вводу/виводу замінюється єдиним сигналом AEN. Природно, в циклі обміну в режимі ПДП бере участь тільки той пристрій вводу/виводу, який заздалегідь запитав ПДП і якому ПДП було надане. Тому ніяких конфліктів між пристроями вводу/виводу через таку спрощену адресацію не виникає.

Мал. 2.12. Структура зв'язків запиту/надання ПДП на магістралі ISA.